Microchip and STAR-Dundee Create First SpaceVPX -Compliant Development Platform Featuring Radiation-Tolerant FPGAs and SpaceFibre Technology

Platform enables developers to implement new high-speed data transfer technology for modern spacecraft using Microchip’s radiation-tolerant RTG4™ FPGAs

Microchip Technology Inc. via its Microsemi subsidiary, collaborated with STAR-Dundee to create an evaluation platform that implements SpaceFibre technology, which was recently recognized by the VITA Standards Organization (VSO) as a control-and-data plane option for its SpaceVPX interconnect standard.

The SpaceFibre standard is already published as a very high-speed serial link standard by the European Cooperation for Space Standardization.

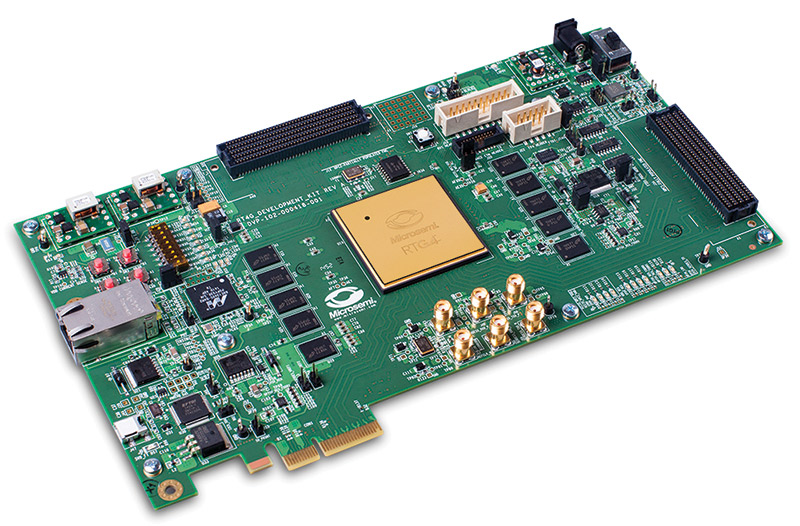

The STAR-Dundee 3U SpaceVPX demonstration board speeds the development of flexible, high-speed SpaceVPX (VITA-78)-compliant data-networking systems for space applications. As the first of its kind to feature FPGAs that are immune to radiation-induced configuration changes, the development board uses the unique architecture of Microchip’s RTG4 devices to optimize performance while providing systems with a critical additional level of failure protection in space.

As SpaceVPX increases in popularity for use in payload processor and system controller modules, the SpaceVPX-compliant platform utilizing SpaceFibre technology and Microchip’s RTG4 FPGAs provides the following benefits:

Offers much higher performance than was possible with the previous SpaceWire data transmission standard

Supports increasing demand for data to be transmitted between boards and systems onboard modern spacecraft

Reduces mass and in return reduces cost by operating over electrical or fiberoptic cables

Improves system reliability by enabling virtual planes to carry data, control and management information

Protects spaceflight systems from configuration upsets in harsh radiation environments through built-in radiation mitigation techniques

Microchip’s non-volatile RTG4 FPGAs include logic resources, digital signal processing math blocks and 24 on-chip high-speed serializer/deserializer (SERDES) lanes and can be used to implement data-handling and processing subsystems that have multi-Gbit/s SpaceFibre interfaces..

Microchip Technology Inc.

www.microchip.com